Hiệu chỉnh mất tương thích độ khuếch đại và mất tương thích thời gian của bộ chuyển đổi tương tự số đan xen thời gian (TIADC) với các tín hiệu ở các miền Nyquist sử dụng nguyên tắc lọc nhiễu thích nghi

269 lượt xemDOI:

https://doi.org/10.54939/1859-1043.j.mst.77.2022.137-149Từ khóa:

All-digital feed-forward calibration; Sub-sampling TIADCs; FPGA implementation; ANC principle.Tóm tắt

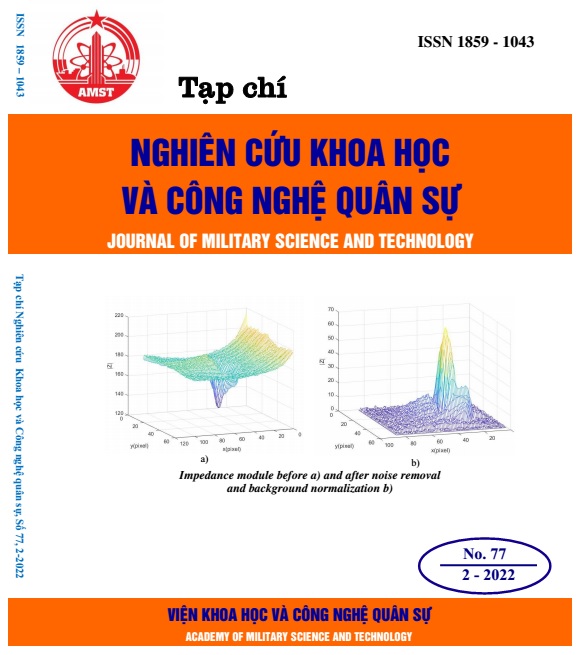

Bài báo trình bày một kỹ thuật hiệu chỉnh hoàn toàn ở miền tín hiệu số cho bộ chuyển đổi tương tự số, lấy mẫu xen kẽ theo thời gian của các sub-ADC (TIADC). Việc hiệu chỉnh mất tương thích độ khuếch đại và mất tương thích thời gian của TIADC bằng kỹ thuật ước lượng được thiết kế dựa trên nguyên tắc bộ lọc thích nghi loại bỏ nhiễu (ANC). Trong nguyên tắc ANC này, có hai tầng để ước lượng mất tương thích thời gian và độ khuếch đại giữa các sub- ADC, trong đó cấu trúc phân tầng của hiệu chỉnh và ước lượng được đề xuất đảm bảo đạt được hiệu suất cao. Ngoài các tín hiệu vào ở vùng Nyquit đầu tiên, các tín hiệu vào tại các vùng Nyquist khác nhau cũng được thử nghiệm. Kết quả là kỹ thuật hiệu chỉnh của chúng tôi thực hiện được trên tất cả các vùng Nyquist khác nhau. Kết quả đã cải thiện được mức của SNDR và SFDR lần lượt là 19dB và 49dB. Hơn nữa, tổng hợp thiết kế với mô phỏng phần cứng được thực hiện trên nền tảng FPGA Xilinx Kintex-7 chỉ tiêu thụ 7,36% tài nguyên phần cứng của chip FPGA và giảm biên độ của các hài mất tương thích xuống mức -87 dB. Đồng thời, thời gian hội tụ của việc ước lượng chỉ bằng 1/3 thời gian của một số tác giả khác.

Tài liệu tham khảo

[1] . H. L. Duc et al.,“Fully digital feed forward background calibration of clock skews for sub-sampling tiadcs using the polyphase decomposition,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 64, No. 6 (2017), pp. 1515–1528.

[2] . B. Razavi, “Design Considerations for Interleaved ADCs,” IEEE Journal of Solid-State Circuits, Vol. 48, No. 8 (2013), pp. 1806–1817.

[3] . J. G. Proakis and D. G. Manolakis, “Digital Signal Processing: Principles, Algorithms and Applications,” Upper Saddle River, New Jersey (2007).

[4] . P. Diniz, “Adaptive Filtering: Algorithms and Practical Implementation,” Kluwer international series in engineering and computer science, Springer (2008).

[5] . H. Le Duc et al., “A Fully Digital Background Calibration of Timing Skew in Undersampling TI-ADC,” IEEE 12th International in New Circuits and Systems Conference (NEWCAS) (2014).

[6] . D. Camarero et al., “Mixed-Signal Clock-Skew Calibration Technique for Time-Interleaved ADCs,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 55, No. 11 (2008), pp. 3676–3687.

[7] . A. Haftbaradaran and K. W. Martin, “A sample-time error compensation technique for time-interleaved adc systems,” IEEE in Custom Integrated Circuits Conference (CICC) (2007), pp. 341–344.

[8] . H. Le Duc et al., “All-Digital Calibration of Timing Skews for TIADCs Using the Polyphase Decomposition,” IEEE Transactions on Circuitsand Systems II: Express Briefs, Vol. 63 (2016).

[9] . J. Matsuno et al., “All-Digital Background Calibration Technique for Time-Interleaved ADC Using Pseudo Aliasing Signal,” IEEE Transactions on Circuits andSystems I: Regular Papers, Vol. 60, No. 5 (2013), pp.1113–1121.

[10] . P. Satarzadeh et al., “A parametric polyphase domain approach to blind calibration of timing mismatches for M-channel time-interleaved ADCs,” Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS), (2010), pp. 4053–4056.

[11] . V. Divi and G. W. Wornell, “Blind Calibration of Timing Skew in Time-Interleaved Analog-to-Digital Converters,” IEEE Journal of Selected Topics in Signal Processing, Vol. 3, No. 3 (2009), pp. 509–522.

[12] . S. Huang and B. Levy, “Blind Calibration of Timing Offsets for Four-Channel Time-Interleaved ADCs,” IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 54, No. 4 (2007), pp. 863–876.

[13] . Le Duc Han, Thi Kim Phuong Dinh, Van-Phuc Hoang, and Duc Minh Nguyen. “All-digital background calibration of gain and timing mismatches in time-interleaved ADCs using adaptive noise canceller,” AEU-International Journal of Electronics and Communications 114 (2020): 152999.

[14] . J. A. McNeill et al., “Split ADC’ Calibration for All-Digital Correction of Time-Interleaved ADC Errors,” IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 56, No. 5 (2009), pp. 344–348,.

[15] . C. Vogel et al., “Adaptive blind compensation of gain and timing mismatches in M-channel time-interleaved ADCs,” 15th IEEE International Conference on Electronics, Circuits and Systems ICECS (2008), pp. 49–52.

[16] . S. Chenet al., “All-digital calibration of timing mismatch error in time-interleaved analog-to-digital converters,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 25, No. 9 (2017), pp. 2552–2560.

[17] . P. P. Vaidyanathan, “Multirate Systems and Filter Banks,” Upper Saddle River, NJ, USA:Prentice-Hall, Inc.(1993).